# APPENDIX B

# NONLINEAR MICROWAVE CIRCUIT DESIGN USING MULTIHARMONIC LOAD-PULL SIMULATION TECHNIQUE\*

This appendix presents practical applications of the multiharmonic load-pull simulation technique to the design of nonlinear microwave circuits. A systematic scheme using multiharmonic load-pull simulation explores the effects of each harmonic termination on the circuit performance and finds the optimal load at each harmonic. The circuit performance can significantly be improved following this systematic design procedure. This approach provides an efficient means of nonlinear microwave circuit design. Its advantages are illustrated for the design of two power amplifiers and a frequency doubler.

#### **B-1 INTRODUCTION**

With the rapid development of wireless communication in recent years, the quality of the nonlinear circuits, such as power amplifiers, oscillators, and frequency doublers, is becoming an increasingly critical component of the entire communication system. A good design of such nonlinear circuits can significantly improve the performance of the system and reduce its cost.

The harmonic-balance (HB) technique has widely been used for nonlinear microwave circuit design since its implementation in commercial CAD software. Many new applications have been developed for the HB method such as stability analysis [1, 2] and load-pull simulation [3]. Load-pull techniques and harmonic load tuning have been used successfully for large-signal device characterization and nonlinear circuit design (e.g., [4–7]). However,

<sup>\*</sup>This appendix is based on Qian Cai, Jason Gerber, Chao-Ren Chang, and Ulrich L. Rohde, "Nonlinear Microwave Circuit Design Using Multi-harmonic Load-Pull Simulation Technique," *Int. J. Microwave Millimeter-Wave Computer-Aided Eng.*, 1999.

the design procedure has never been described systematically. This prevents or restricts the practical usage of the load-pull techniques.

Here we present a systematic scheme to use the load-pull technique efficiently in nonlinear microwave circuit design. Multiharmonic load-pull simulation using the HB method is used as a vehicle for our presentation. Response contours are simulated by sampling the corresponding harmonic impedance of the selected tuner connected to the input or output port. Optimal harmonic impedances are located from the response contours. A step by step design procedure is described.

Our process can be classified into two major steps: finding the optimal loading at each harmonic and checking the power levels of higher harmonics. By checking the power levels of higher harmonics, we can readily see the effects of higher harmonic loading on the circuit performance. Further steps are carried out based on the investigation of the higher harmonic loading effects. It is a very effective way for microwave engineers to achieve good, if not the best, results in nonlinear circuit design.

The multiharmonic load-pull simulation is presented in Section B-2. Applications of multiharmonic load-pull simulation to nonlinear circuit design are addressed in Section B-3. The circuit designs of two power amplifiers and a frequency doubler are demonstrated.

# B-2 MULTIHARMONIC LOAD-PULL SIMULATION USING HARMONIC BALANCE

#### B-2-1 Formulation of Multiharmonic Load-Pull Simulation

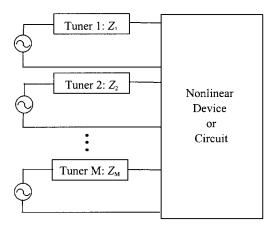

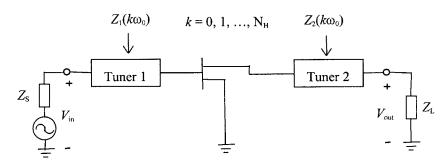

The multiharmonic load-pull simulation is implemented within the nonlinear simulator, Microwave Harmonica [8], which uses an efficient HB technique [9]. The circuit topology for the multiharmonic load-pull simulation can be sketched generally as Figure B-1, where M tuners are placed at the M external ports considered. The formulation can generally be expressed as

$$E(X, Z) = 0 (B-1)$$

where *E* is the vector of HB errors, *X* is the set of all harmonic state variables, and *Z* is the set of harmonic loads on all external ports. The *k*th subvector of *E* can be written

$$E_k(X, Z) = A(k\omega_0, Z)\Phi(X, Z) + B(k\omega_0, Z)\Psi(X, Z) + D(k\omega_0, Z)$$

(B-2)

where  $0 \le k \le N_H(N_H)$  is the number of harmonics used in the simulation), A and B are circuit matrices, D is a set of driving functions, and  $\Phi$  and  $\Psi$  are, respectively, the harmonic vectors of instantaneous voltages v and currents i at the nonlinear subnetwork ports.

The harmonic loads Z can be written in the following matrix form:

$$Z = \begin{bmatrix} Z_{1}(0\omega_{0}) & Z_{1}(1\omega_{0}) & \dots & Z_{1}(N_{H}\omega_{0}) \\ Z_{2}(0\omega_{0}) & Z_{2}(1\omega_{0}) & \dots & Z_{2}(N_{H}\omega_{0}) \\ \vdots & \vdots & \vdots & \vdots \\ Z_{M}(0\omega_{0}) & Z_{M}(1\omega_{0}) & \dots & Z_{M}(N_{H}\omega_{0}) \end{bmatrix}$$

(B-3)

Figure B-1 Circuit topology for multiharmonic load-pull simulation.

where M is the number of external ports considered and  $Z_i(k\omega_0)$  is the load at the kth harmonic and the ith port with  $(0\omega_0)$  representing the dc component. The purpose of multiharmonic load-pull simulation is to find the optimal harmonic loading with respect to the design specifications. An impedance sampling method is used in our implementation of multiharmonic load-pull simulation. Only one component of Z is sampled at the defined impedance plane while the others are kept constant at each step. The HB simulation is performed at each sampling point to solve for the circuit responses specified. After the simulations are finished at all sampling points, load-pull contours are plotted on the Smith Chart and then the optimal point is located.

#### **B-2-2** Systematic Design Procedure

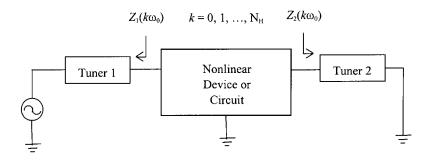

Without losing generality, and for easy illustration, we consider the two-port circuit shown in Figure B-2, where tuners are placed at the source and load ports. The impedance sampling is achieved by adjusting the tuner parameters, which can be described as follows.

$$R_i(k\omega_0)$$

—The resistance at the *i*th tuner and the *k*th harmonic,  $i=1,2,$  and  $k=1,2,\ldots,$   $N_H$ .

$X_i(k\omega_0)$ —The reactance at the *i*th tuner and the *k*th harmonic,  $i=1,2,$  and  $k=1,2,\ldots,$   $N_H$ .

In order to obtain a uniform sampling of points, the tuner impedance is mapped to a reflection coefficient using a reference impedance  $Z_r$  and the mapping equation

$$\Gamma_i(k\omega_0) = \frac{Z_i(k\omega_0) - Z_r}{Z_i(k\omega_0) + Z_r}$$

(B-4)

The impedance sampling is transferred to two sweeps: the magnitude of  $\Gamma_i(k\omega_0)$  [ $\Gamma_i(k\omega_0)$ ] from 0 to 1 and the angle of  $\Gamma_i(k\omega_0)$  [ $\angle\Gamma_i(k\omega_0)$ ] from 0° to 360°. Only the impedance at one selected tuner i and one harmonic k, that is,  $\Gamma_i(k\omega_0)$ , is allowed to be tuned at a time and the other harmonic impedances are fixed at any meaningful values. In the following presentation we select  $Z_r = 50~\Omega$ .

Figure B-2 Circuit schematic of a typical two-port nonlinear circuit.

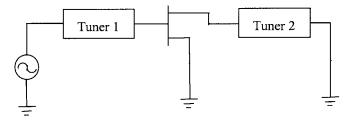

The systematic design procedure can be described as follows:

- Step 1: Start load-pull simulation by sampling the impedance at the fundamental frequency  $Z_i(\omega_0)$  and find the optimal load  $Z_{io}(\omega_0)$ .

- Step 2: Fix  $Z_i(\omega_0)$  at  $Z_{io}(\omega_0)$  and check the output spectrum to see the effects of higher harmonic loads on the circuit responses. If the effects of higher harmonic loads are significant, let k = 2, and go on to Step 3. Otherwise stop.

Figure B-3 Flowchart of design procedure using multiharmonic load-pull simulation.

Step 3: Perform load-pull simulation by sampling the kth harmonic impedance  $Z_i(k\omega_0)$  and find the optimal load  $Z_{io}(k\omega_0)$ .

Step 4: Fix  $Z_i(k\omega_0)$  at  $Z_{io}(k\omega_0)$  and check the output spectrum to see the effects of higher harmonic loads on the circuit responses. If the effects of higher harmonic loads are significant, let k = k + 1, and go to Step 3. Otherwise stop.

This procedure can be repeated for all the tuners to achieve the optimal solution. It can be summed up as a load-pull simulation and spectrum-checking process. The flowchart in Figure B-3 illustrates this procedure.

#### B-3 APPLICATION OF MULTIHARMONIC LOAD-PULL SIMULATION

#### **B-3-1** Narrowband Power Amplifier Design

Two power amplifiers, Amplifier 1 and Amplifier 2, are considered. The amplifiers are designed to operate at 0.5 GHz. The circuit schematic used for amplifier design is shown in Figure B-4. A Siemens power MESFET CLY10 [10] is used in our design. The MESFET is modeled by the modified Materka model [11] implemented in Microwave Harmonica [8]. Without losing generality, and for easy illustration, we fix all harmonic impedances of Tuner 1 (at the source port) at 50  $\Omega$  and tune Tuner 2 (at the load port) for both examples. Six harmonics are used in the HB simulation.

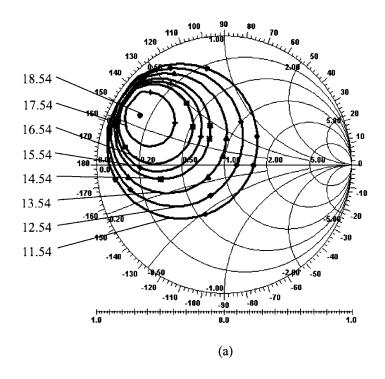

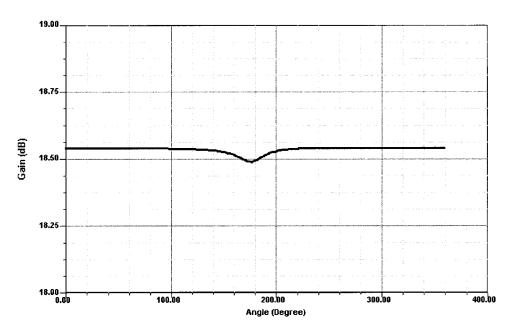

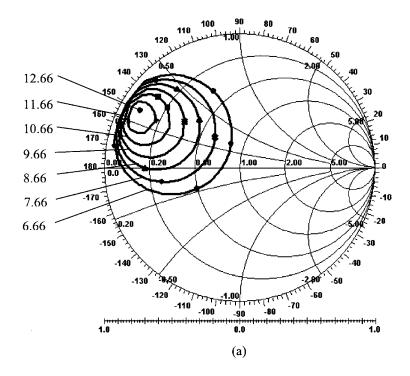

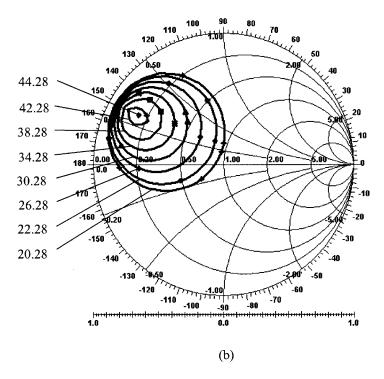

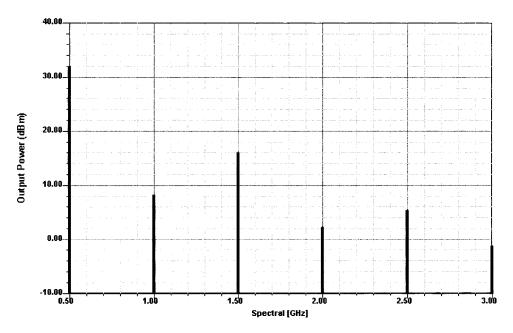

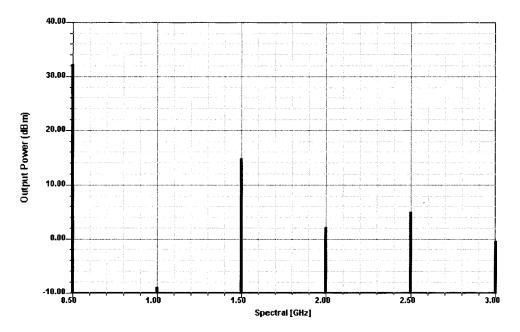

In Amplifier 1, the MESFET is biased at  $V_{gs} = -1.3$  V and  $V_{ds} = 5$  V, and the amplifier is designed as a normal Class A type with an input power of 10 dBm. Following the procedure described above, we perform load-pull simulation by sampling  $Z_2(\omega_0)$  of Tuner 2 while other harmonic impedances of Tuner 2 are fixed at 50  $\Omega$ . The load-pull contours of power gain and power-added efficiency (PAE) are plotted in Figure B-5. The optimal load  $Z_{20}(\omega_0)$  is found to be 9.07 + j12.99, at which the power gain is 18.54 dB and PAE is about 20%. The output power spectrum at this point is plotted in Figure B-6. By checking the output power spectrum of Figure B-6, we can see that the power levels at all higher harmonics are very small. Therefore, the higher harmonic loads will not have significant effects on the amplifier performance. To verify this conclusion, we perform load-pull simulation by sampling  $Z_2(2\omega_0)$  of Tuner 2 while  $Z_2(\omega_0)$  is fixed at  $Z_{20}(\omega_0)$ . It is found that the best performance with respect to power gain and PAE is obtained for purely reactive second-harmonic loads, which is consistent with the results obtained by Berini et al. [5]. The output power versus the phase of  $\Gamma_2(2\omega_0)$  is shown in Figure B-7, from which we can see that the influence of  $Z_2(2\omega_0)$  is very small and our conclusion is justified.

Figure B-4 Circuit topology for the amplifier design using multiharmonic load-pull simulation.

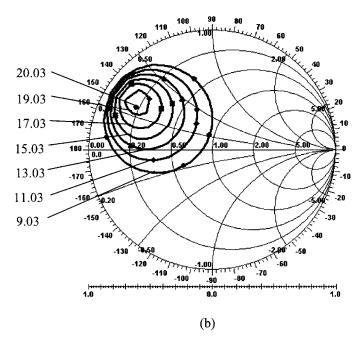

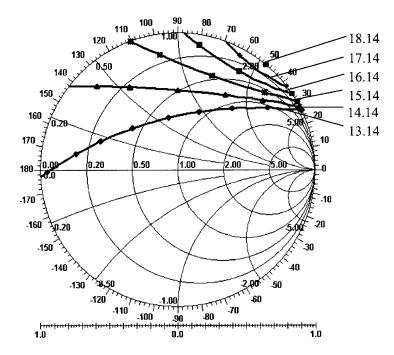

Figure B-5 Load-pull contours of (a) power gain (dB) and (b) PAE (%) of Amplifier 1 obtained from fundamental load-pull simulation.

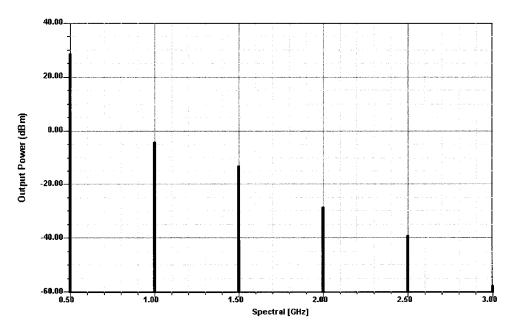

**Figure B-6** Output power spectrum of Amplifier 1 when  $Z_2(\omega_0) = Z_{20}(\omega_0)$ .

In order to illustrate the effects of higher harmonic loading on the amplifier performance, the MESFET is biased at  $V_{gs} = -2.0 \text{ V}$  and  $V_{ds} = 5 \text{ V}$ , and the input power is increased to 20 dBm in Amplifier 2. Figure B-8 shows the contours of power gain and PAE at the fundamental load-pull simulation. The optimal load  $Z_{20}(\omega_0)$  is 4.31 + j13.30 for power gain (12.66 dB)

Figure B-7 Power gain versus the phase of  $\Gamma_2(2\omega_0)$  for Amplifier 1.

**Figure B-8** Load-pull contours of (a) power gain (dB) and (b) PAE (%) of Amplifier 2 obtained from fundamental load-pull simulation.

and 7.61 + j13.11 for PAE (44.28%). Though a compromise between the power gain and PAE can be obtained, we select 7.61 + j13.11 as our  $Z_{20}(\omega_0)$  and consider the PAE as the primary specification throughout the following process. The output spectrum at this point is shown in Figure B-9, which indicates that the output power levels at higher harmonics are significant, and thus the higher harmonic loads are critical to the amplifier performance.

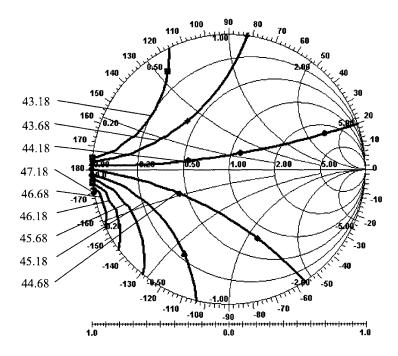

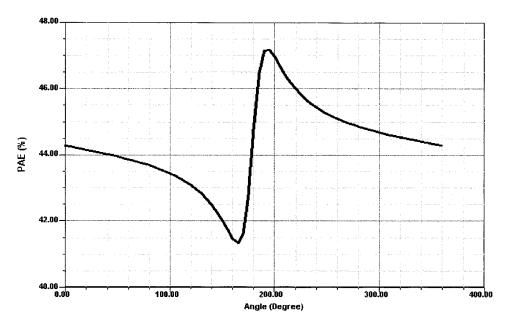

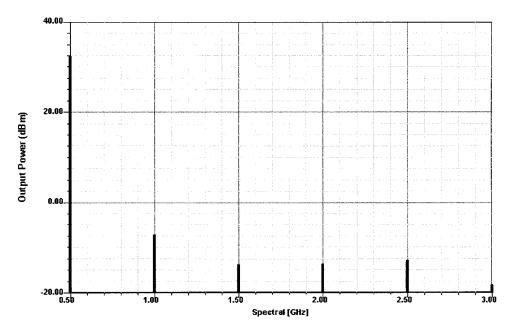

By fixing  $Z_2(\omega_0)$  at 7.61 + j13.11 and sampling  $Z_2(2\omega_0)$ , we perform the second-harmonic load-pull simulation. The contours of PAE are shown in Figure B-10, which also indicates that the best point for the second-harmonic load will be pure reactance near the short-circuit point. The effect of the phase of  $\Gamma_2(2\omega_0)$  on PAE is shown in Figure B-11. The optimal value of  $Z_{2o}(2\omega_0)$  is -j6.58, where the phase of  $\Gamma_2(2\omega_0)$  is 195°. The PAE is improved from 44.28% to 47.18%. The output power spectrum at  $Z_2(\omega_0) = 7.61 + j13.11$  and at  $Z_2(2\omega_0) = -j6.58$  is shown in Figure B-12. From Figure B-12, we can see that the amplifier performance can be further improved by a proper third-harmonic load. The third-harmonic load-pull simulation is carried out by sampling  $Z_2(3\omega_0)$  while  $Z_2(\omega_0)$  and  $Z_2(2\omega_0)$  are maintained at their optimal values.  $Z_{2o}(3\omega_0)$  is found to be -j65.16 at which the value of PAE is 47.66%. Following the same procedure, we perform load-pull simulations up to the sixth harmonic. The results are as follows:

| Harmonic Load    | Optimal Value |

|------------------|---------------|

| $Z_2(\omega_0)$  | 7.61 + j13.11 |

| $Z_2(2\omega_0)$ | -j6.58        |

| $Z_2(3\omega_0)$ | -j65.16       |

| $Z_2(4\omega_0)$ | -j2.18        |

| $Z_2(5\omega_0)$ | -j28.81       |

| $Z_2(6\omega_0)$ | -j23.32       |

**Figure B-9** Output power spectrum of Amplifier 2 when  $Z_2(\omega_0) = Z_{20}(\omega_0)$ .

$\textbf{Figure B-10} \quad \text{Load-pull contours of PAE (\%) of Amplifier 2 obtained from the second-harmonic load-pull simulation.}$

Figure B-11 PAE versus the phase of  $\Gamma_{\!2}\!(2\omega_0)$  for Amplifier 2.

**Figure B-12** Output power spectrum of Amplifier 2 when  $Z_2(\omega_0) = Z_{20}(\omega_0)$  and  $Z_2(2\omega_0) = Z_{20}(2\omega_0)$ .

The PAE is 48.13% and power gain is 12.38 dB at the final design. The output power spectrum of the final design is shown in Figure B-13, which indicates that the output power levels at the second and higher harmonics have been suppressed significantly compared to the ones shown in Figure B-9.

#### **B-3-2** Frequency Doubler Design

The circuit schematic shown in Figure B-14 is used for the frequency doubler design. The MESFET is biased at pinchoff, with  $V_{gs} = -1.9$  V and  $V_{ds} = 5$  V. The frequency of the input waveform is 5 GHz and the input power is 3 dBm. Six harmonics are considered in the HB simulation. Both  $Z_S$  and  $Z_L$  are 50  $\Omega$ . The conversion gain (CG) and the spectral purity (SP), are considered as the design specifications, calculated, respectively, by

$$CG = \frac{P_L(2\omega_0)}{P_{out}(\omega_0)}$$

(B-5)

and

$$SP = \frac{P_L(2\omega_0)}{N_H}$$

$$\sum_{k=1, k\neq 2} P_L(k\omega_0)$$

(B-6)

where  $P_L$  is the power delivered to the load  $Z_L$  and  $P_{avs}$  is the available source power. In addition to the load-pull simulation, we also perform source-pull simulation in the design.

Figure B-13 Output power spectrum of Amplifier 2 at the final design.

Note that the harmonic impedance  $Z_i(k\omega_0)$  is the tuner impedance without the load  $Z_L$  or the source impedance  $Z_S$ , and  $\Gamma_i(k\omega_0)$  is the reflection coefficient of the tuner only in this design example.

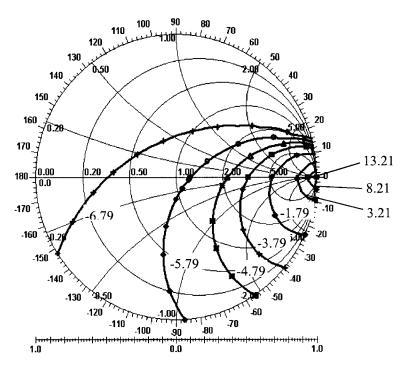

First, the fundamental load-pull simulation is performed by sampling  $\Gamma_2(\omega_0)$  at Tuner 2 while the impedances of all harmonics at Tuner 1 and other harmonic impedances of Tuner 2 are fixed at  $0~\Omega$ . The contours of SP with respect to  $\Gamma_2(\omega_0)$  are plotted in Figure B-15, from which we can see that the optimal tuner impedance is infinity, which means that the fundamental harmonic component of the output waveform should be completely reflected by an open circuit. We select  $1 \angle 0$  as the optimal point  $[\Gamma_{2o}(\omega_0)]$ , at which the SP is 13.21 dB and the CG is -9.75 dB. The second-harmonic load-pull simulation is performed by

Figure B-14 Circuit topology for frequency doubler design using multiharmonic load-pull simulation.

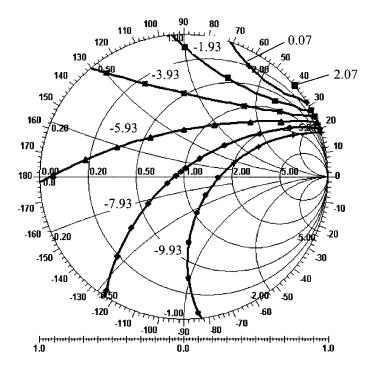

sampling  $\Gamma_2(2\omega_0)$  with  $\Gamma_2(\omega_0)$  being fixed at  $\Gamma_{2o}(\omega_0)$ . The contours of SP with respect to  $\Gamma_2(2\omega_0)$  are plotted in Figure B-16. The  $\Gamma_{2o}(2\omega_0)$  is found to be  $1 \angle 50$ , at which the SP is improved from 13.21 to 18.14 dB and the CG from -9.75 to -5.89 dB. Following the same procedure, the load-pull simulation is performed up to the sixth harmonic. It is found that all the optimal harmonic impedances of Tuner 2 are infinity, except for the second harmonic, at which the optimal impedance is found to be j127.23. At the end of the load-pull simulation, the SP is 25.28 dB and the CG is -5.87 dB. The CG cannot be improved very much by tuning the harmonic impedances of Tuner 2.

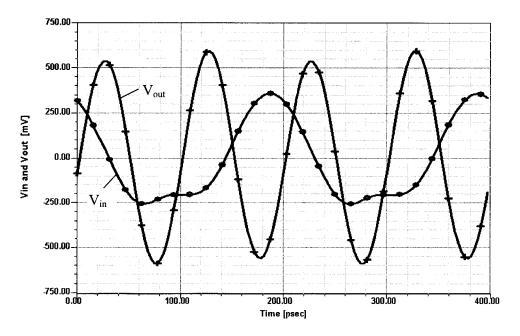

The source-pull simulation is carried out by sampling the harmonic impedances of Tuner 1 using the same procedure as load-pull simulation with all the harmonic impedances of Tuner 2 being fixed at their optimal values. It is found that the most dominant harmonic impedance of Tuner 1 is the fundamental harmonic impedance. The optimal impedances at other harmonics of Tuner 1 turn out to be 0. The contours of CG with respect to  $\Gamma_1(\omega_0)$  obtained by fundamental source-pull simulation with other harmonic impedances of Tuner 1 set to 0  $\Omega$  are plotted in Figure B-17. The  $\Gamma_{1o}(\omega_0)$  is found to be 1  $\angle$  40. The CG is significantly improved from –5.87 to 2.07 dB with a minor 0.5-dB degradation of spectral purity. The input and output voltage waveforms under the optimal termination conditions are shown in Figure B-18, from which we can see that the frequency of the output voltage is doubled to 10 GHz with a reasonable gain. The distortion of the input voltage waveform is due to the reflection of the higher-order harmonic voltages.

**Figure B-15** Contours of spectral purity (dB) with respect to the fundamental impedance of Tuner 2  $[\Gamma_2(\omega_0)]$  obtained from fundamental load-pull simulation of the frequency doubler.

**Figure B-16** Contours of spectral purity (dB) with respect to the second-harmonic impedance of Tuner  $2 \left[ \Gamma_2(2\omega_0) \right)$  obtained from the second-harmonic load-pull simulation of the frequency doubler.

**Figure B-17** Contours of conversion gain (dB) with respect to the fundamental impedance of Tuner 1  $[\Gamma_1(\omega_0)]$  obtained from fundamental source-pull simulation of the frequency doubler.

**Figure B-18** Input and output voltage waveforms of the frequency doubler under the optimal termination conditions.

#### **B-4 CONCLUSIONS**

We have presented practical applications of multiharmonic load-pull simulation to the design of nonlinear microwave circuits. A systematic procedure has been addressed for effective circuit design. It has been demonstrated that the circuit performance can be improved significantly by a proper design of harmonic loads. This method can be applied to the design of nonlinear microwave circuits such as the power amplifier and frequency doubler to achieve the optimal solution and to utilize the maximum potential of the devices employed in the circuits.

#### B-5 NOTE ON THE PRACTICALITY OF LOAD-PULL-BASED DESIGN

From the standpoint that the wireless designer cannot have access to too many design aids, load-pull-based design techniques can serve as a valuable addition to the wireless designer's toolbox. We caution, however, that the current surge of interest in load-pull design techniques may owe as much to fashion and wishful thinking as it does to the practical achievability of the improved hardware performance that load-pull analysis may predict. Realizing the gain, PAE, and spectral-purity predictions of analyses like those presented here depends on the realization of optimum, controllable terminations at the signal fundamental *and its significant harmonics*—a nontrivial design challenge to say the least.

#### **ACKNOWLEDGMENT**

The work on which this appendix is based was sponsored under the DARPA MAFET Thrust 1 program, Agreement No. MDA972-96-3-0001. Partial contributions of Dr. Solti Peng of TI, Dallas, Texas, to some of the materials presented here are gratefully acknowledged.

#### **REFERENCES**

- 1. V. Rizzoli and A. Neri, "State of the Art and Present Trends in Nonlinear Microwave CAD Techniques," *IEEE Trans. Microwave Theory Tech.*, MTT-36, 343–365, 1988.

- J. Gerber and C. R. Chang, "Application of the Harmonic-Balance Method to the Stability Analysis of Oscillators," *IEEE MTT-S International Microwave Symposium Digest*, pp. 1587– 1590, 1997.

- 3. Q. Cai, J. Gerber, and S. Peng, "A Systematic Scheme for Power Amplifier Design Using a Multi-harmonic Load-Pull Simulation Technique," *IEEE MTT-S International Microwave Symposium Digest*, 1998.

- R. Hajji, F. Beauregard, and F. Ghannouchi, "Multitone Power and Intermodulation Load-Pull Characterization of Microwave Transistors Suitable for Linear SSPAs Design," *IEEE Trans. Microwave Theory Tech.*, MTT-45, 1093–1099, 1997.

- P. Berini, M. Desgagn, F. Ghannouchi, and R. G. Bosisio, "An Experimental Study of the Effects

of Harmonic Loading on Microwave MESFET Oscillators and Amplifiers," *IEEE Trans. Microwave Theory Tech.*, MTT-42, 943–950, 1994.

- M. A. Khatibzadeh and H.Q. Tserng, "Harmonic Tuning of Power FETs at X-Band," *IEEE MTT-S International Microwave Symposium Digest*, pp. 989–992, 1990.

- B. Kopp and D. D. Heston, "High-Efficiency 5-watt Power Amplifier with Harmonic Tuning," IEEE MTT-S International Microwave Symposium Digest, pp. 839–842, 1988.

- Microwave Harmonica Reference Manual, Ansoft Corporation, Compact Software Division, Elmwood Park, NJ.

- 9. V. Rizzoli, C. Cecchetti, A. Lipparini, and F. Mastri, "General-Purpose Harmonic Balance Analysis of Nonlinear Microwave Circuits Under Multitone Excitation," *IEEE Trans. Microwave Theory Tech.*, MTT-36, 1650–1660, 1988.

- 10. Einzelhalbleiter Discrete and RF Semiconductors, Siemens Data Book 02.97, 1997.

- A. Materka and T. Kacprzak, "Computer Calculation of Large-Signal GaAs FET Amplifier Characteristics," *IEEE Trans. Microwave Theory Tech.*, MTT-33, 129–135, 1985.

# 射频和天线设计培训课程推荐

易迪拓培训(www.edatop.com)由数名来自于研发第一线的资深工程师发起成立,致力并专注于微波、射频、天线设计研发人才的培养;我们于2006年整合合并微波EDA网(www.mweda.com),现已发展成为国内最大的微波射频和天线设计人才培养基地,成功推出多套微波射频以及天线设计经典培训课程和ADS、HFSS等专业软件使用培训课程,广受客户好评;并先后与人民邮电出版社、电子工业出版社合作出版了多本专业图书,帮助数万名工程师提升了专业技术能力。客户遍布中兴通讯、研通高频、埃威航电、国人通信等多家国内知名公司,以及台湾工业技术研究院、永业科技、全一电子等多家台湾地区企业。

易迪拓培训课程列表: http://www.edatop.com/peixun/rfe/129.html

# 射频工程师养成培训课程套装

该套装精选了射频专业基础培训课程、射频仿真设计培训课程和射频电路测量培训课程三个类别共 30 门视频培训课程和 3 本图书教材;旨在引领学员全面学习一个射频工程师需要熟悉、理解和掌握的专业知识和研发设计能力。通过套装的学习,能够让学员完全达到和胜任一个合格的射频工程师的要求…

课程网址: http://www.edatop.com/peixun/rfe/110.html

## ADS 学习培训课程套装

该套装是迄今国内最全面、最权威的 ADS 培训教程, 共包含 10 门 ADS 学习培训课程。课程是由具有多年 ADS 使用经验的微波射频与通信系统设计领域资深专家讲解,并多结合设计实例,由浅入深、详细而又全面地讲解了 ADS 在微波射频电路设计、通信系统设计和电磁仿真设计方面的内容。能让您在最短的时间内学会使用 ADS, 迅速提升个人技术能力,把 ADS 真正应用到实际研发工作中去,成为 ADS 设计专家...

课程网址: http://www.edatop.com/peixun/ads/13.html

## HFSS 学习培训课程套装

该套课程套装包含了本站全部 HFSS 培训课程,是迄今国内最全面、最专业的 HFSS 培训教程套装,可以帮助您从零开始,全面深入学习 HFSS 的各项功能和在多个方面的工程应用。购买套装,更可超值赠送 3 个月免费学习答疑,随时解答您学习过程中遇到的棘手问题,让您的 HFSS 学习更加轻松顺畅···

课程网址: http://www.edatop.com/peixun/hfss/11.html

# CST 学习培训课程套装

该培训套装由易迪拓培训联合微波 EDA 网共同推出,是最全面、系统、 专业的 CST 微波工作室培训课程套装, 所有课程都由经验丰富的专家授 课,视频教学,可以帮助您从零开始,全面系统地学习 CST 微波工作的 各项功能及其在微波射频、天线设计等领域的设计应用。且购买该套装, 还可超值赠送3个月免费学习答疑…

# HFSS 天线设计培训课程套装

套装包含6门视频课程和1本图书,课程从基础讲起,内容由浅入深, 理论介绍和实际操作讲解相结合,全面系统的讲解了 HFSS 天线设计的 全过程。是国内最全面、最专业的 HFSS 天线设计课程,可以帮助您快 速学习掌握如何使用 HFSS 设计天线, 让天线设计不再难…

课程网址: http://www.edatop.com/peixun/hfss/122.html

# 13.56MHz NFC/RFID 线圈天线设计培训课程套装

套装包含 4 门视频培训课程,培训将 13.56MHz 线圈天线设计原理和仿 真设计实践相结合,全面系统地讲解了13.56MHz线圈天线的工作原理、 设计方法、设计考量以及使用 HFSS 和 CST 仿真分析线圈天线的具体 操作,同时还介绍了 13.56MHz 线圈天线匹配电路的设计和调试。通过 该套课程的学习,可以帮助您快速学习掌握 13.56MHz 线圈天线及其匹 配电路的原理、设计和调试…

详情浏览: http://www.edatop.com/peixun/antenna/116.html

# 我们的课程优势:

- ※ 成立于 2004年, 10 多年丰富的行业经验,

- ※ 一直致力并专注于微波射频和天线设计工程师的培养,更了解该行业对人才的要求

- ※ 经验丰富的一线资深工程师讲授,结合实际工程案例,直观、实用、易学

## 联系我们:

- ※ 易迪拓培训官网: http://www.edatop.com

- ※ 微波 EDA 网: http://www.mweda.com

- ※ 官方淘宝店: http://shop36920890.taobao.com

易迪拓信训 官方网址: http://www.edatop.com